目前,随着多媒体应用的普及,千兆位以太网已经发展成为主流网络技术。大到成千上万人的大型企业,小到几十人的中小型企业,在建设企业局域网时都会把千兆位以太网技术作为首选的高速网络技术。千兆位以太网技术甚至正在取代ATM技术,成为城域网建设的主力军。

E1接口采用PCM编码方式。符合G.703标准,通过75Ω同轴电缆或120Ω双绞线进行非对称或对称传输。在电信网中有着广泛应用。

将高速的千兆位以太网信号与低速的E1信号结合起来,实现以太网与E1信号的复用。既满足了用户对大带宽、高容量数据的传输要求,又提供了E1信号接入功能,实现电话业务及其他专用通信系统的接入功能。

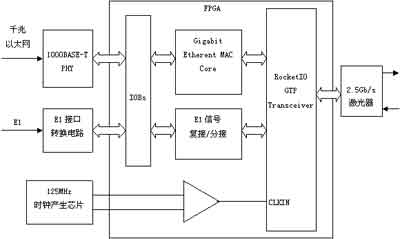

系统构成整个系统主要由E1接口单元、以太网接口单元、FPGA单元以及光接口单元构成。E1接口单元主要完成E1信号的接口转换,以太网接口单元主要通过外部PHY芯片实现物理层功能,再通过GMII接口实现与FPGA以太网媒体接入控制器对接。吉比特收发器通过用户接口将以太网数据和经过码速调整后的E1信号形成16b并行数据,再经过16b/20b编码形成2.5Gb/s的数据流送入到光接口单元,光接口单元完成光/电转化,实现信号的光纤传输。系统框图如图1所示。

图1 系统构成框图

E1接口单元的设计

在E1信道中,一般每8位组成一个时隙,32个时隙组成一个帧,16个帧组成一个复帧。在一个帧中,TS0主要用于传送帧定位信号(FAS)、CRC-4(循环冗余校验)和对端告警指示,TS16主要传送随路信令(CAS)、复帧定位信号和复帧对端告警指示,TS1~TS15和TS17~TS31共30个时隙则用来传送话音或数据等信息。如果采用公共信道信令(CCS)模式,TS16就失去了传送信令等信号的用途,TS1~TS31共31个时隙可传送话音或数据等信息。如果采用无帧模式,E1信道将不成帧,而作为一个透明的话音或数据等信息传输通道。一个E1信道可传送N个64Kb/s的话音或数据等信息通道。在随路信令(CAS)模式,N为1~30;在公共信道信令(CCS)模式,N为1~31,而在无帧模式时,N为32。

发送方向:E1信号首先经过接口变压器,然后送入单/双变换电路,完成单双变换后送入FPGA芯片。FPGA将E1线路接口单元送来的HDB3数据送入时钟提取模块,提取出E1时钟,并且将HDB3数据转换成NRZ数据,NRZ数据经码速调整后复用成一路125Mb/s数据流,然后送入RocketIO GTP Transceiver 发送接口单元中,和千兆位以太网信号一起进行线路编码,最后形成2.5Gb/s的数据流送入到激光器进行光线路编码进行传输。

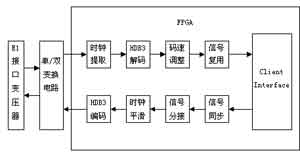

接收方向:信号经光纤传输后到达接收端,首先恢复成电信号送入到RocketIO GTP Transceiver接收单元中,经时钟提取、信号同步、解码、信号分接,时钟平滑后分接出E1数据流,再经HDB3编码后送入到单双变换电路完成双/单变化,经接口变压器后进行传输。原理框图如图2所示。

图2 E1接口原理框图

千兆位以太网接口单元设计

千兆位以太网利用原以太网标准所规定的全部技术规范,其中包括CSMA/CD协议、以太网帧、全双工、流量控制以及IEEE 802.3标准中所定义的管理对象。千兆位以太网的关键技术是千兆位以太网的MAC层和以太网接口的实现。

1 GMII (Gigabit MII)

GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mb/s。同时兼容MII所规定的10/100Mb/s工作方式。接口信号定义如表1所示。

表1 GMII接口信号定义

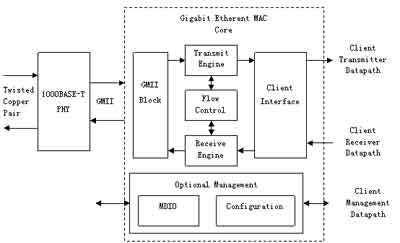

2 Virtex-5以太网媒体接入控制器

在Virtex-5 FPGA中,以太网媒体接入控制器(以太网MAC)模块提供了专用的以太网功能,它和Virtex-5 RocketIO GTP收发器以及SelectIO技术相结合,能够让用户与各种网络设备进行连接。在Virtex-5器件中,以太网MAC模块作为一个硬件块集成在FPGA内部。吉比特以太网MAC功能框图如图3所示。

图3 吉比特以太网MAC功能框图

(1)客户端接口

发送器的客户端接口将帧传送给以太网MAC。当接收到的数据小于最短的以太网帧长度时,发送器将该数据加长,并且保持最小的帧间距;可以增加间隔的长度,还可以通过配置发送器在帧中添加一个帧检验序列。一个单独的流控制接口允许你生成暂停帧。在半双工模式下,信号发送之间存在冲突,在有效冲突情况下,需要进行帧重发。

接收器接口检验传入帧和信号帧误差。这里分别提供了好帧信号和坏帧信号。还可以通过配置以太网MAC以便在检测到有效的暂停帧之后,暂停和重新启动帧传输。

客户端接口的数据的宽度通常是8位或者16位。8位接口主要针对标准的以太网应用,它利用一个125MHz的时钟产生1000Mb/s的数据传输速率。当使用16位模式时,可以在不提高客户端接口时钟频率的条件下将数据传输速率提高到2000Mb/s。

(2)控制接口

每个以太网MAC有一个可选的管理数据I/O(MDIO)接口。它允许对外部PHY的管理寄存器和以太网MAC中PCS/PMA内部的物理接口管理寄存器进行访问。

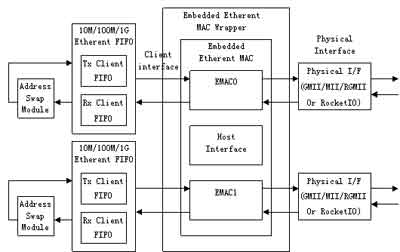

3 Virtex-5以太网MAC封装

图4显示了一个HDL封装的模块结构图,它可以从Xilinx的COREGenerator工具中获得。

图4 Virtex-5以太网MAC封装的模块结构图

以太网MAC是一个具有162个端口和79个参数的复杂组件。封装文件让你可以仅对特定应用所需端口的参数和接口轻松进行设置。它们的另外一个优势是简化了时钟和物理I/O资源的使用。

以太网MAC封装。在最低级别,实体化一个单独的或者双以太网MAC,同时在CORE Generator GUI中将它的属性设置成你偏好的选项。所有未使用的输入端口接地,未使用的输出端口保持开路状态。

模块级别的封装。在下一层级,对物理接口以及所要求的时钟资源进行实体化。这包括用于串行接口的RocketIO GTP收发器。同时针对你的配置对时钟进行优化,并且利用时钟将输出同步到你的设计。

LocalLink级别的封装。在该级别,将FIFO添加到客户端发送器和接收器接口。FIFO能够处理接收时坏帧的丢失并且以半双工模式对帧重新传输。LocalLink可以作为后端接口使用。

RocketIO GTP Transceiver

RocketIO是一种高速的串行收发器,采用两对差分对来进行数据的发送和接收,可以实现两个单工或一对全双工的数据传输。RocketIO支持622Mb/s~3.75Gb/s的全双工传输速率,还具有8b/10b编解码(平衡编码)、时钟生成及恢复等功能。Aurora协议是为专有上层协议或行业标准的上层协议提供透明接口的第一款串行互连协议,可用于高速线性通路之间的点到点串行数据传输,同时其可扩展的带宽,为系统设计人员提供了所需要的灵活性。

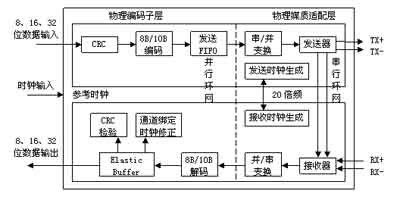

1 PMA和PCS层

RocketIO包括PMA(物理媒介适配层)和PCS(物理编码子层)两个子层,其内部结构如图5所示。其中PMA子层主要用于串行化和解串,PCS主要包括线路编码和CRC校验编码。

图5 PMA、PCS内部结构框图

PMA子层中集成了SERDES,发送和接收缓冲,时钟发生器及时钟恢复电路。SERDES是一个串并转换器,负责FPGA中本地的32位并行数据(也可以是16位或8位)与RocketIO接口的串行数据之间的转换。采用串行数据收发,可以在高频条件下很好地避免数据间的串扰。时钟发生器及时钟恢复电路用于将时钟与数据绑定发送,以及将时钟从接收到的数据流中恢复出来,从而避免了在高速传输条件下时钟与数据分开传输所带来的时钟抖动等问题。

PCS子层负责8b/10b编码解码和CRC校验,并集成了负责channel绑定和时钟修正的弹性缓冲。8b/10b编码可以避免数据流中出现连0连1的情况,便于时钟的恢复。channel绑定通过在发送数据流中加入P字符来将几个RocketIO通道绑定成一个一致的并行通道,从而来提高数据的吞吐率。最多支持24个通道的绑定。弹性缓冲可以解决恢复时钟与本地时钟的不一致问题,并进行数据率的匹配,从而使得channel绑定成为可能。对Rocket IO模块的配置,可以通过下面两种方式进行:静态特性可以通过HDL代码设置;动态特性可以通过RocketIO的原语端口进行配置。

2 时钟合成器

在实际设计中,高性能的通信质量要求有高稳定性和高精度的时钟源,而抖动和频偏是衡量时钟源的两个重要指标。RocketIO内部的工作时钟需要将输入时钟经过数十倍的倍频,但其可容忍的时钟偏差为40ps,因此建议选择高精度的差分时钟。当RocketIO在2.5Gb/s以上时,参考时钟应采用差分输入方式(例如LVDS、LVPECL),由专用差分时钟引脚输入,然后引到相同或相邻通道中RocketIO的参考时钟输入端;当RocketIO在2.5Gb/s以下时,不要使用FPGA内部的DCM模块来产生参考时钟,因为经过DCM倍频的时钟会引入较大的抖动,使RocketIO的接收锁相环无法稳定地锁定发送时钟。

当高精度时钟输入到FPGA中后,吉比特发送器对参考时钟输入管脚REFCLK的信号完成20倍倍频操作后,来作为自己的工作时钟。同样,该倍频器已集成在芯片中,不需要额外的组件。RXRECCLK和REFCLK二者之间没有固定的相位关系,且都为专用时钟信号,不能连接到其他管脚上作为他用。当使用4字节或1字节数据接收路径时,RXUSRCLK和RXUSRCLK2具有不同的频率,但是频率低的时钟下降沿要和频率高的时钟下降沿对齐。同样的关系也适用于TXUSRCLK和TXUSRCLK2信号。

Rocket IO采集数据的同步时钟则是通过时钟/数据恢复电路来提取的,该电路由一个单片的PLL集成块实现,不需要任何外部组件。恢复电路从接收的数据流中提取出时钟的频率和相位,并通过20倍分频后送到输出管脚RXRECCLK上。

时钟和数据恢复器:如果没有数据存在,时钟/数据恢复器(CDR)电路会自动锁相到参考时钟上。为了使操作达到最优性能,参考时钟的精度必须在100×10-6之内。同时要满足供电系统的低噪声。如果有数据,则恢复电路会自动同步锁相到输入数据上。

发送器:发送器模块包括发送接口、8b/10b编码器、不均匀控制、发送FIFO、串行器、发送终端以及预加重电路。

接收器:接收器模块主要包括解串器、接收终端和8b/10b解码器。

光接口单元

光接口单元主要包括光发射模块和数字光接收放大器模块。它们的功能分别是将电脉冲信号变换成光脉冲信号和将接收到的衰减变形的微弱光脉冲信号通过光/电转换成电脉冲信号。光发射模块把符合数字光纤通信系统传输性能要求的光脉冲波形从光源组件的尾纤发射出去。光接收放大器模块由PIN+FET和放大电路组成。它将微弱光脉冲信号经O/E转换,并给予足够的放大,还原成原来的数字脉冲信号。

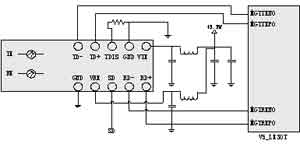

本设计选用飞通2.5Gb/s光模块,中心波长1550nm。传输距离可达40km。参考电路如图6所示。

图6 与光模块连接示意图

结束语

本文设计的基于Xilinx FPGA的千兆位以太网及E1信号的光纤传输系统采用Xilinx XC5VLX30T芯片,通过以太网测试仪和数据误码仪对本系统分别进行性能测试,测试结果满足设计要求,系统工作稳定。从而实现了千兆位以太网信号和E1信号的接入功能,为用户搭建了一个大容量、多业务的传输平台。